실리콘

Why silicon?

1. 풍부한 자원 -> 저렴한 재료(Ge에 비해)

2. SiO2(insulator, diffusion barrier, dielectric layer...) -> 비교적 간단한 공정을 통해 안정된 산화막 생성 가능

3. 우수한 온도 특성 -> Ge에 비해 녹는점이 높아 고온공정 가능

4. 고순도화 용이 -> single crystal 실리콘을 제작하기 용이함

실리콘(Si) 구조: two interpenetrating face-centered cubic(FCC), diamond structure

실리콘 결정면 특성: Conductivity -> (100) > (110) > (111) *MOS device에 (100)을 주로 사용

Density, Growth -> (111) > (110) > (100) *(111)이 가장 저렴, Bipolar device에 주로 사용

Single crystal silicon vs Poly-crystal silicon: 가격 -> 단결정>다결정

Conductivity -> 단결정>다결정

*반도체 산업은 부가가치가 높으므로 성능이 좋은 단결정 실리콘을 사용

실리콘 웨이퍼 생산

1. 고순도 실리콘(Semiconductor-Grade Silicon, SGS) 생산

1) Metallugical Grade Silicon(MGS) 생산: SiO2(모래)를 C(석탄, 환원제)와 함께 고온(1800°C) 에서 녹임

SiO2(s) + 2C(s) -> Si(l) + 2CO

Si(l)은 Al, Fe와 같은 불순물을 포함하고 있음, 전기적 특성 나쁨

2) Electronic Grade Silicon(EGS) 생산: 불순물을 제외한 Si과만 반응하는 HCl을 사용하여 고순도화 시킴

Si(s) + 3HCl(g) -> SiHCl3(g) + H2(g)

3) Siemens Process: poly-Si rod를 1100°C에서 SiHCl3를 CVD시켜 99.9999999(9N) 고순도 poly-Si 고체로 만듦

2SiHCl(g) + 2H2(g) -> 2Si(s) + 6HCl(g)

2. 단결정 실리콘 Ingot 제조

(1) Czochralski(CZ) Method: 녹은 poly-Si에 seed SC Si가 붙은 rod를 담구고 천천히 돌리면서 꺼내 SC Si 성장

Rod를 꺼내는 속도로 ingot diameter 제어, doping을 통해 p,n-type Si 생성 가능

장점: 큰 size의 Silicon ingot 생성 가능, 비교적 저렴 -> 현재 사용중인 공정

단점: crucible로 인한 impurities(Oxygen, Carbon), Doping했을 때 axial&radial dopant concentration 일정하지 않음

(2) Float Zone(FZ): poly-Si를 녹이지 않고 bar형태의 poly-Si의 끝에 SC-Si seed를 놓고 RF coil이 천천히 올라가며 heating을 통해 SC-Si를 성장시킴

장점: 고순도 가능(crucible 사용X, 불순물이 coil 따라 올라가서 모임)

단점: CZ에 비해 비쌈, 큰 size의 Si 생성X(8 inch limited) -> 현재 잘 사용되지 않는 공정

3. 잉곳 Grind & Wafer Flat

1) Grind: 잉곳의 size가 다른 끝부분을 자르고, Diameter grind를 통해 균일한 지름 생성

2) Flat: Flat or notch를 생성

*웨이퍼 표면 구조를 구별하기 위해 flat을 만들어 표시함, but 웨이퍼를 자르면 그만큼 손실이 생기므로

8인치 웨이퍼 부터 flat 대신 notch를 사용

4. Wafer Slicing

(1) Blade: 원통 blade에 잉곳을 넣어 diamond saw로 한 장 씩 slicing

장점: wafer surface가 비교적 flat하고 smooth -> 후에 연마 공정 단축 가능

단점: 시간이 오래걸림 -> 생산성 저하

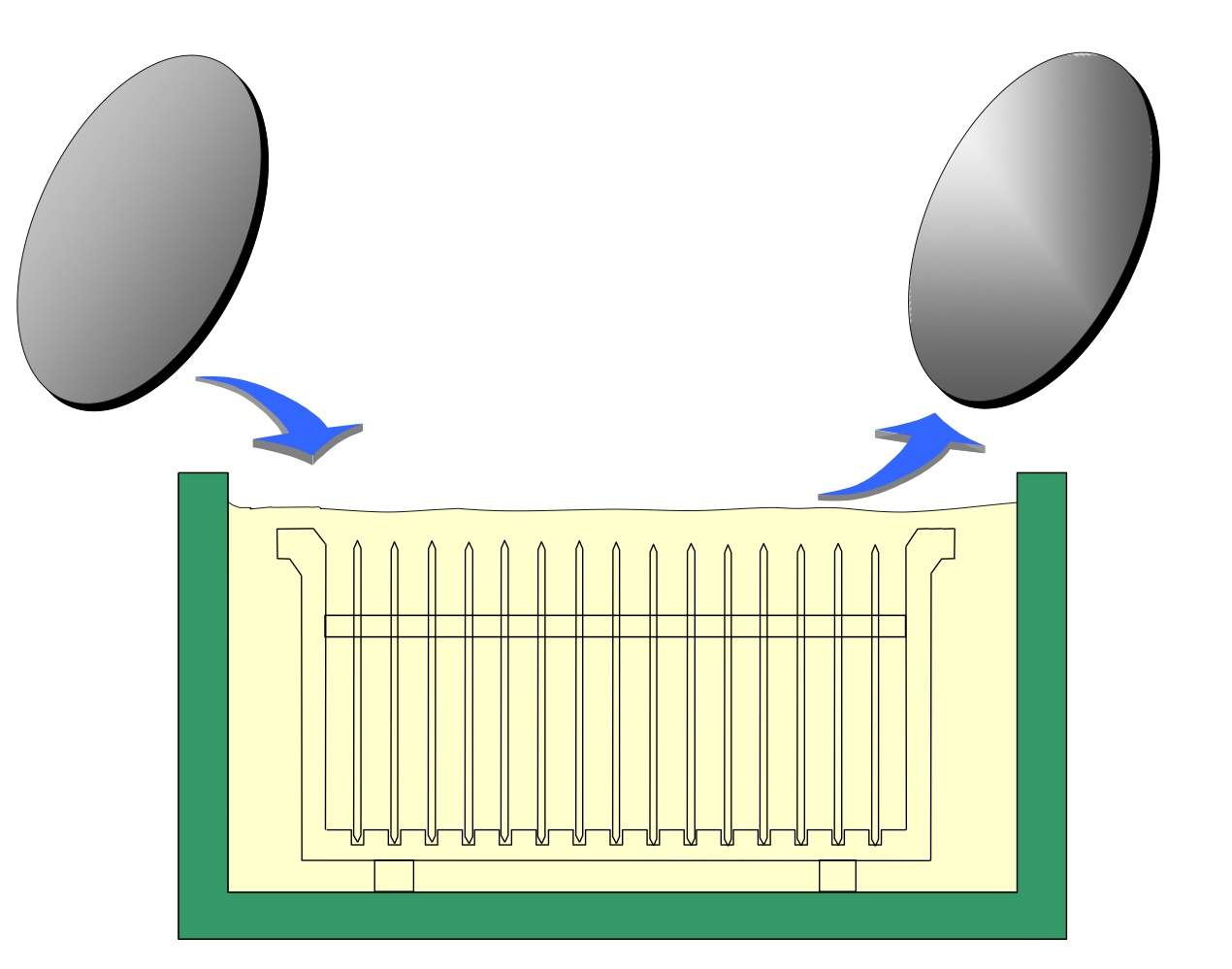

(2) Wire saw: diamond saw를 겹겹이 배치해 한번에 여러 장 slicing

장점: Thickness loss 줄임, 한 번 cutting에 수 백 웨이퍼 생산 -> 생산성 증가, 현재 사용중인 공정(300mm wafer)

단점: 비교적 less flat하고 less smooth -> 연마 공정 시간 증가

5. Wafer Lapping & Edge Grind

1) Lapping: slurry를 포함하는 grain(Al2O3, SiC)를 넣고 표면 연마 -> wafer surface damage 제거, flatness 상승

*grinding: 박혀있는 연마재로 표면을 갈아냄

lapping: 연마재를 위에 올려 문지름

2) Edge grind: wafer edge를 갈아 smooth radius 생성

6. Chemical Etch & CMP

1) Chemical Etch: wafer 표면의 contaminations 제거, Acid(HNO3/HF) or Alkaline(KOH) 사용

2) Chemical Mechnical Polishing(CMP): 마지막 flat 공정, 고운 slurry를 사용하여 atomic scale 표면연마 -> 표면 광택

*다양한 공정 후에 flatness 혹은 etch를 목적으로 사용하므로 매우 중요

'반도체 전공정 기본' 카테고리의 다른 글

| 반도체 공정 - (4) - 1 식각 공정(Parameters, Plasma Dry Etch) (0) | 2024.07.10 |

|---|---|

| 반도체 공정 - (3) - 2 포토 공정(장비, Parameters) (0) | 2024.07.08 |

| 반도체 공정 - (3) - 1 포토 공정(과정, PR) (0) | 2024.07.05 |

| 반도체 공정 - (2) 산화막 공정 (1) | 2024.06.08 |

| 반도체 공정 - (1) 웨이퍼 공정(클리닝) (0) | 2024.05.31 |