Doping

Si기판에 13족(p형 도핑) or 15족(n형 도핑) 원소를 도핑해 자유전자 or 정공을 생성.

=> 반도체에 전기적 특성을 좋게함

1. (Thermal) Diffusion

열 에너지로 dopant 입자를 Si 기판 안으로 diffusion 시켜 도핑

과정

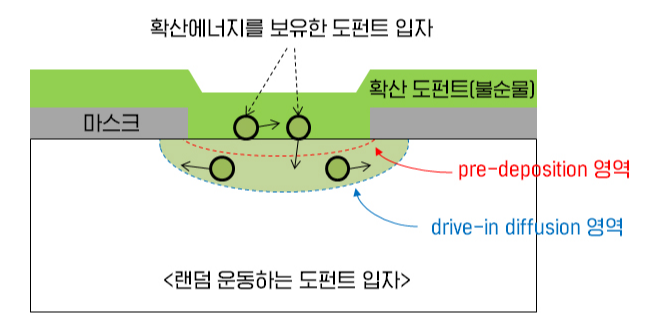

1) Pre-deposition: 800~1000°C에서 dopant를 기판 위에 얇게 증착

2) Drive in: 1000~1200°C에서 dopant를 Si기판 안으로 diffusion 시킴

3) Activation: 온도를 살짝 더 올려 Si 원자와 dopant사이에 bond를 형성

특징

1. Diffusion mask로 SiO2 or Si3N4 사용(PR은 고온 공정에서 사용 불가)

2. vertical한 diffusion 뿐만 아니라 lateral diffusion도 있으므로 untarget area도 도핑

2. Ion Implantation

Ion implanter에 의해 이온이 가속되어 wafer에 부딪히며 물리적으로 wafer에 implant 되며 도핑

과정

1) Ion source: vaccum chamber에서 high voltage를 가해 dopant gas로 부터 positive ion 생성

=> 다양한 종류의 ion 생성, 추후 과정에서 분류

2) Extraction assembly: biased extraction electrode로 ion beam 형태로 모으고 extraction 시킴

3) Ion Analyzer: 자기장으로 ion을 휘게 하며, 무게에 따라 휘어짐이 다름을 이용해 원하는 ion만 분류

4) Acceleratior: Ion들이 focus lense에 의해 beam으로 모이고 강한 전기장에 의해 가속됌

5) Process Camber: wafer를 기울이거나 돌리면서 target area에 ion implant doping

Thermal Diffusion vs Ion Implantation

고온 저온

Isotropic Anisotropic

Bad Uniformity Good Uniformity

Bad control(depth) Good control(depth)

이온주입 장단점

| 장점 | 단점 |

| 저온 공정 가능 고순도의 이온 주입 가능 정확한 dopant 농도 조절 가능 정확한 위치에 도핑 가능(깊이 조절) lateral한 doping 적음(anisotropic) |

장비가 비쌈 생산성이 낮음(공정 속도 느림) Channeling, Shadowing effect 물리적 충돌로 인해 damage 발생 |

Parameter

Implant current: Ion의 수, 도핑 농도를 조절

Implant time: Ion Implanter의 scan speed, wafer의 rotation speed로 조절

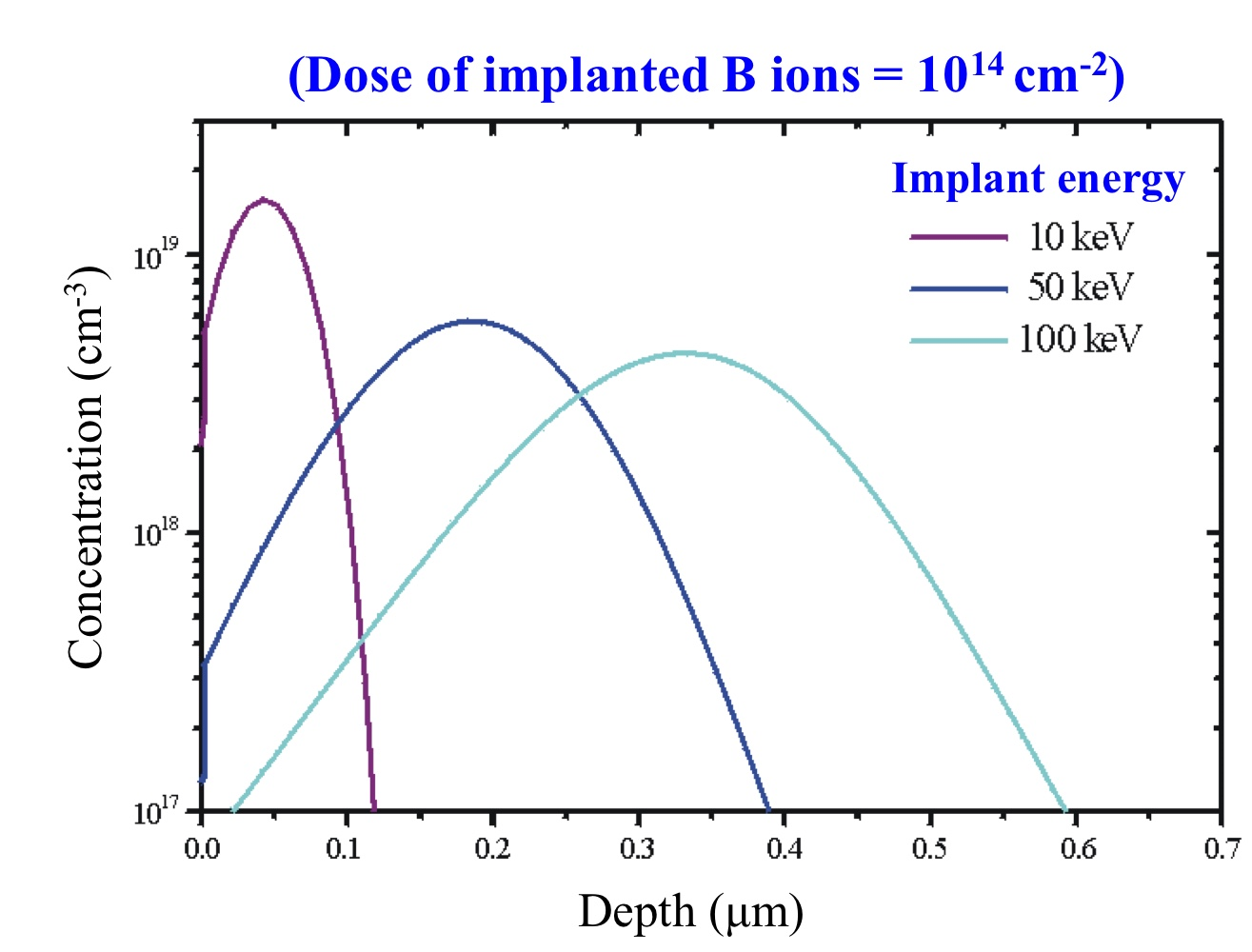

Implant energy: 도핑 깊이 조절(에너지가 0이 되면 정지)

Implant angle: 도핑 깊이 조절(다른 원자와 충돌하며 정지)

Dose: 이온 농도(단위 면적당, 단위 시간당 주입되는 양)

Atoic mass: dopant 무게에 따라 깊이 다름(가벼울 수록 깊이)

적은 도핑 농도 & 얕은 도핑

=> Low energy(느린 속도), Low dose(적은 양), 빠른 scan speed, 무거운 이온

높은 도핑 농도 & 깊은 도핑

=> High energy(빠른 속도), High dose(많은 양), 느린 scan speed, 가벼운 이온

Issue & Solution

Issue: 1) Wafer charging

positive ion이 masking layer위에 쌓이며 +전하를 가짐

=> doping 방해

해결책: Plasma electron flood:

Ion beam에 primary electron을 쏴서 secondary electron을 생성하고,

secondary electron이 ion beam과 같이 나오며 charging area를 중성화 시킴

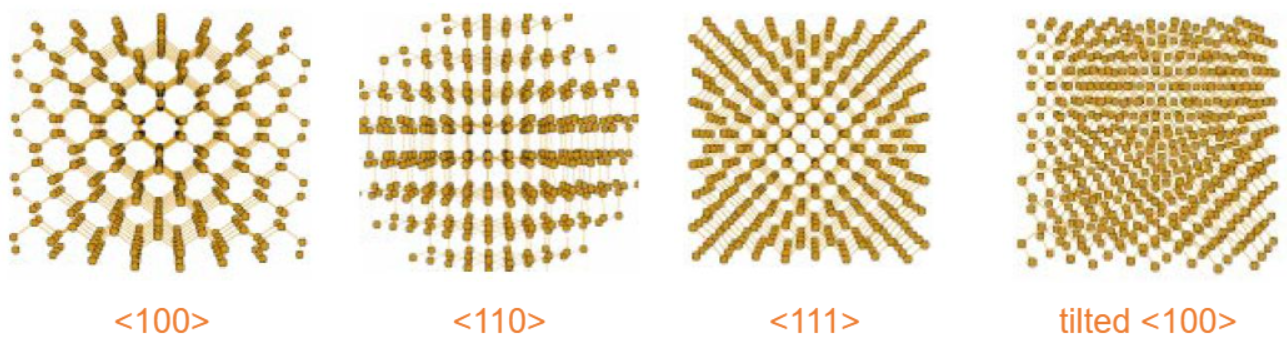

Issue: 2) Channeling

Implant된 이온이 Si 원자와 충돌하지 않고 그대로 통과해버림

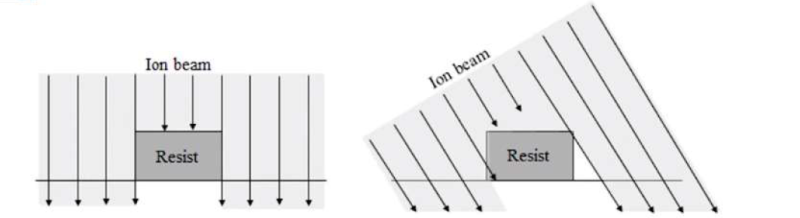

해결책: 1) Wafer Tilt

wafer를 기울여 Si의 배열 밀도를 높여 Si atom과의 충돌 확률을 늘림

=> but 과도한 tilting은 shadowing effect 유발

해결책: 2) Screen oxide layer

SiO2를 표면에 형성해 dopant energy를 충분히 낮춘 다음 Si wafer에 도달시켜 channeling 방지

=> but, 공정 step 증가로 인해 생산성 저하

해결책: 3) Pre-amorphization

Si기판 표면에 damage를 줘 amorphous Si 생성

dopant energy를 충분히 낮춘 다음 Si wafer에 도달시켜 channeling 방지

=> but, 표면에 강한 damage를 가하므로 성능 저하 유발

Issue: 3) Damage

Ion implatation은 기판에 물리적으로 충격을 가해 damage를 줌

해결책: Annealing

열에너지를 줘서 dopant와 Si 원자를 activation시켜 damage를 회복시킴

'반도체 전공정 기본' 카테고리의 다른 글

| 반도체 공정 - (7) 증착 공정 (0) | 2024.07.30 |

|---|---|

| 반도체 공정 - (6) 금속 배선 공정 (0) | 2024.07.30 |

| 반도체 공정 - (4) - 2 식각 공정(물질 별 식각) (0) | 2024.07.11 |

| 반도체 공정 - (4) - 1 식각 공정(Parameters, Plasma Dry Etch) (0) | 2024.07.10 |

| 반도체 공정 - (3) - 2 포토 공정(장비, Parameters) (0) | 2024.07.08 |